# **Организация ЭВМ и систем.** Конспект лекций. Рабочая версия.

Кустарев П.В., Довгий П.С., Скорубский В.И. Кафедра Вычислительной Техники СПЕГУ ИТМО Санкт-Петербург 2010-2011г.

## ОГЛАВЛЕНИЕ.

| Осно | овные понятия                                       | 2  |

|------|-----------------------------------------------------|----|

| 1.1  | Понятие ЭВМ                                         | 2  |

| 1.2  | Понятие архитектуры и организации ЭВМ               | 4  |

| 1.3  | Виды организации и архитектуры ЭВМ.                 | 6  |

| 2 (  | Эрганизация ЭВМ                                     | 10 |

| 2.1  | Логическая организация ЭВМ                          | 10 |

| 2.2  | Структурно-функциональный базис ЭВМ                 | 12 |

| 2.3  | Базовые принципы организации ЭВМ фон Неймана        | 16 |

| 3 (  | Эрганизация процессора                              | 21 |

| 3.1  | Классификация процессоров                           | 21 |

| 3.2  | Модель тракта данных (datapath) процессора          | 24 |

| 3.3  | Функциональные блоки процессора                     | 27 |

| 3.4  | Функциональная организация однотактового процессора | 29 |

| 3.5  | Реализация однотактового процессора.                |    |

| 3.6  | Использование однотактовых процессоров              |    |

| 3.7  | Организация мультитактового процессора              |    |

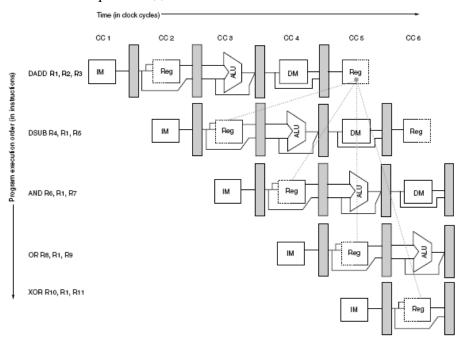

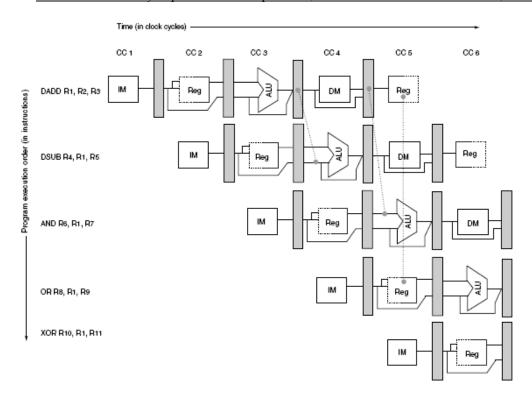

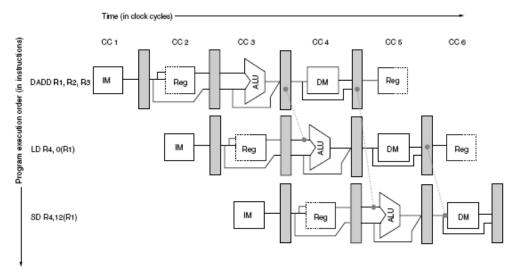

| 3.8  | Организация конвейеров                              | 53 |

Основные понятия.

#### 1.1 Понятие ЭВМ

Вычислительная машина (ВМ, компьютер) — это искусственная техническая система, предназначенная для обработки данных под управлением наборов команд.

Непосредственно с понятием ЭВМ связаны, а иногда заменяют его, другие понятия. Наиболее часто употребляемые из них:

Процессор — центральный аппаратный блок ЭВМ, непосредственно осуществляющий обработку данных. В настоящее время основным типом процессоров являются цифровые программно управляемые процессоры. Такие процессоры построены на базе цифровых электронных схем и используют для обработки данных методы булевой алгебры и двоичной арифметики.

Bычислительный комплекс (BK) — несколько ЭВМ, имеющих общие (разделяемые структурные блоки, например, общую память.

Вычислительная система (BC) – аппаратно-программная система из нескольких ЭВМ, жестко взаимосвязанных аппаратно и логически, и, обычно, пространственно локализованных. ЭВМ в составе ВС являются неотъемлемыми частями для решения единой задачи.

Вычислительная сеть (ВСТ) — система из нескольких ЭВМ, функционирующих автономно, но связанных между собой каналами передачи данных, которые могут использоваться для обмена данными, для синхронизации работы ЭВМ и для организации совместного решения единой задачи (подобно ВС). ВСТ могут быть пространственно децентрализованными, но также могут быть локализованными, например, в рамках одной электронной платы (Network on a Board) или даже в одной микросхеме (Network on a Chip).

#### 1.2 Типы ВМ.

- 1) ВМ может иметь различную физическую природу:

- Электронные ВМ (ЭВМ) ВМ, имеющая в физической основе электронную схему это на сегодня наиболее распространенные типы ВМ. Они в свою очередь могут делиться на цифровые ЭВМ и аналоговые ЭВМ.

- Механические, оптические, пневматические, биологические и другие, в том числе комбинированные типы ВМ данные типы ВМ в настоящее время менее распространены, чем ЭВМ в силу неразвитости или неэффективности технологии их производства на современном этапе. Однако могут рассматриваться как варианты перспективных типов ВМ (например, ведутся активные исследования в области оптоэлектронных ВМ).

- 2) ВМ «настраиваются» на исполнение требуемого алгоритма путём исполнения поданных им команд. Множество команд, которое ВМ может понять и выполнить называют *набором команд ВМ (instruction set)*. Существуют различные типы ВМ, для которых понятие «команда ВМ» интерпретируется по разному:

- а) Команды представлены в виде некоторых кодов, которые последовательно исполняются ВМ. В процессе исполнения команд внутренние структура и правила функционирования ВМ не меняются – можно говорить, что команды для неё – это нечто «внешнее». ВМ с таким принципом работы называют «программноуправляемой ВМ». На сегодняшний момент - это наиболее распространенный тип ВМ. Важно, что программа и алгоритм это не одно и то же: один и тот же алгоритм может быть реализован в виде нескольких различных программ.

- b) У ЭВМ, работающих по принципу реконфигурирования, команды это конфигурационные параметры, которые перенастраивают структуру и режимы функционирования физических средств ВМ на выполнение той или иной функции или алгоритма по обработке данных. Например, можно изменять соединения между блоками ВМ, можно настраивать блоки на реализацию различных функций, можно менять коэффициенты передачи (усиления) электронных каскадов. Данная интерпретация понятия «команда» менее распространено, характерно в основном для специализированных ВМ - для ВМ встраиваемых в приборы, в бортовую аппаратуру и т.п. Однако, в связи с совершенствованием и ростом популярности аппаратуры перепрограммируемой цифровой c структурой (например, программируемых логических интегральных схем - ПЛИС), данный тип ВМ также набирает популярность.

- с) вариант комбинации двух первых вариантов.

В дальнейшем, если не будет особых пометок, речь пойдет об цифровых ЭВМ с комбинированной приоритетом последовательной) последовательной или (c интерпретацией команд.

Примечание:

В литературе предлагается множество различных формулировок понятия ЭВМ (электронная вычислительная машина) 1, компьютер и связанных с ними, от достаточно простых и понятных до вычурных, многие из которых, однако, схожи по своей сути. Например:

Компьютер – это прибор, способный производить вычисления и принимать решения в миллионы или даже в миллиарды раз быстрее человека. Компьютеры обрабатывают данные под управлением наборов команд, называемых компьютерными программами [13].

Компьютер – это машина, которая может решать задачи, выполняя данные ей команды. Последовательность команд, описывающих решение определенной задачи, называется программой [16].

ЭВМ – комплекс электронного оборудования, выполняющий интерпретацию программ в виде физических процессов, назначением которых является реализация математических операций над информацией, представляемой в цифровой форме [2].

ЭВМ – искусственная (инженерная) система, предназначенная для выполнения вычислений на основе алгоритмов. Принципы построения ЭВМ определяются с одной стороны назначением ЭВМ и с другой – элементной базой (набором элементов, которые используются для создания ЭВМ). Основным назначением ЭВМ является выполнение вычислений на основе алгоритмов, и поэтому свойства алгоритмов предопределяют принципы построения ЭВМ или, точнее, ее архитектуру (организацию) [4].

<sup>1</sup> В дальнейшем изложении термины «ЭВМ» и «компьютер» используются как синонимы.

## Понятие архитектуры и организации ЭВМ

В компьютерной литературе связанно (иногда как синонимы, иногда как взаимодополняющие термины) применяются понятия архитектура ЭВМ (computer architecture), организация ЭВМ (computer organization). В ассоциации с этими понятиями используются также термины дизайн (проект) ЭВМ (computer design), аппаратное обеспечение (hardware), программное обеспечение различных уровней (software, firmware, middleware) и другие.

Единого признанного определения для понятий архитектура и организация ЭВМ не существует. Многие специалисты используют их как синонимы. Например, одним из сторонников такого подхода является Э. Таненбаум. В других источниках эти термины имеют различающуюся трактовку, что позволяет более детально определять аспекты, проблемы и задачи, решаемые в рамках создания ЭВМ. Сторонниками такого подхода являются Д. Паттерсон и Д.Хеннеси, В. Столлингс и многие другие. Кроме того, трактовка одного и того же понятия может различаться в зависимости от того, на каком этапе проектирования ЭВМ используется (разработка архитектуры, моделирование, реализация аппаратуры и программного обеспечения).

В данном курсе эти понятия рассматриваются как различные.

## 1.3.1 Архитектура и организация ЭВМ в «широком» и «узком» смыслах.

Можно рассматривать две трактовки понятий архитектура и организация ЭВМ (а также связанных с ними терминов): широкая и узкая.

Понятия в широком смысле используются, чтобы описать и регламентировать процесс проектирования ЭВМ, указывают те обязательные аспекты, этапы и задачи, которые должны быть выделены и проработаны при создании ЭВМ/ВС. Это очень важно, чтобы в процессе создания сложных вычислительных систем были выполнены все фазы, в правильном порядке и с правильными приоритетами и ничего не было упущено. В конечном счёте это определяет качество проектирования.

С другой стороны каждое из понятий в широком смысле затрагивает ВСЕ подсистемы и блоки ЭВМ (хотя и на различном уровне детализации), но не фиксируют перечень элементов ЭВМ/ВС и состав проектных документов, которые относятся к спецификациям архитектуры, организации ЭВМ соответственно. То есть они не позволяют сказать: «Описание архитектуры (организации) ЭВМ должно включать то-то, то-то и то-то». Соответственно их сложно применять в качестве обобщающего регламента для формирования описания ЭВМ. Поэтому для «практических нужд» предложены определения в «узком» смысле.

Понятия в узком смысле нацелены на описание устройства ЭВМ и ее свойств.

## 1.3.2 Понятие архитектуры и организации ЭВМ в «широком» смысле.

ЭВМ может быть описана и проектироваться на различных уровнях:

- На уровне системы команд это так называемый уровень Архитектуры системы команд (Instruction Set Architecture, ISA);

- На уровне (крупных) функциональных блоков и подсистем ЭВМ уровень организации ЭВМ;

- На уровне реализации функциональных блоков в виде программы или аппаратуры - уровень программной, аппаратной или комбинированной (программноаппаратной) реализации ЭВМ (implementation).

Архитектура системы команд (ISA) – совокупность аспектов ЭВМ, видимых программисту. К ней относится организация адресного пространства памяти и периферийных устройств ЭВМ, режимы адресации, типы и форматы операндов, типы и команд, режимы исключений (прерываний), специальные (защищённый, прямого доступа к памяти и т.п.) и другие аспекты. Архитектура системы команд – «внешний вид» ЭВМ, не показывает внутреннего устройства.

Организация ЭВМ рассматривает устройство и проектирование ЭВМ на уровне крупных функциональных боков и подсистем ЭВМ. Например, рассматриваются функции и принципы работы и взаимодействия процессора, блоков памяти, периферийных устройств, шин и т.п. Причём эти принципы (принципы организации ЭВМ) будут похожими как для простейших ЭВМ, так и для высокопроизводительных компьютеров – разница в количественных параметрах. Например, модули памяти ЭВМ, встраиваемой в телефон, и высокопроизводительного сервера различаются количеством запоминающих ячеек, шириной, скоростью передачи данных для шины данных и некоторыми иными параметрами, определяющими ее быстродействие, но внутренняя структура и основные принципы функционирования будут очень похожими.

Кроме аппаратных блоков на уровне организации рассматривают и программные функциональные блоки ЭВМ: супервизоры, операционные системы, драйверы и т.п., но также на высоком уровне, не опускаясь до деталей внутренней организации программного обеспечения.

На уровне организации ЭВМ не рассматривают цифровые электрические схемы (аппаратуру) и программный код (программное обеспечение).

Реализация ЭВМ - воплощение функциональных блоков ЭВМ и связей между ними в виде аппаратуры и/или программного обеспечения.

Архитектура ЭВМ в широком смысле рассматривает общие аспекты, способы объединения процессов и результатов всех уровней проектирования ЭВМ: архитектуры системы команд, организации и реализации.

Конечная цель архитектурного проектирования в широком смысле - объединение компонент и подсистем ЭВМ таким образом, чтобы достигнуть в целом для ЭВМ производительности, энергопотребления, требуемой функциональности, функциональных, технических, конструктивных и коммерческих параметров, вплоть до маркетинговой привлекательности.

То есть архитектура в широком смысле – это совокупность согласованных проектных решений на уровнях системы команд, организации, программно-аппаратной реализации.

Из приведенных выше определений следует понятие Технического проекта (дизайна) ЭВМ в широком смысле – это совокупность спецификаций всех уровней (ISA, организации, реализации), необходимых и достаточных для понимания устройства и функционирования ЭВМ, для ее использования и производства.

## 1.3.3 Понятие архитектуры и организации ЭВМ в «узком» смысле.

Организация ЭВМ в «узком» смысле – все аспекты внутреннего устройства ЭВМ (как аппаратуры, так и программных компонент), которые «не видимы» для пользователя ЭВМ (в большинстве случаев – для программиста, но также и для конечного пользователя) и не оказывают отомкап использования влияния возможности правила (программирования) ЭВМ, если сравнивать их с альтернативными вариантами организации ЭВМ. Например, использование х86-совместимых процессоров одного класса от фирмы Intel или от фирмы AMD не влияет сколько-нибудь ощутимо на правила создания программного обеспечения и на характеристики его функционирования.

Архитектура ЭВМ в «узком» смысле определяет представление и описание возможностей ЭВМ с точки зрения пользователя, например, для программиста разрабатывающего программу на машинно-ориентированном языке, но также, возможно, и для прикладного программиста, и для конечного пользователя, выбирающего настройки программного обеспечения. В этом смысле архитектура в «узком» смысле близка к понятию архитектуры системы команд (ISA).

Архитектура отображает те аспекты структуры и принципы функционирования ЭВМ, которые являются видимыми и/или ощутимыми для пользователя. Например, видимой для программиста будет регистровая модель, ощутимой но не видимой для программиста может быть организация конвейера обработки команд, который будет более эффективен, например, в предсказании переходов, если соблюдать определенные правила построения последовательности машинных команд (на практике эти правила заложены в компилятор программ). Также к архитектуре могут быть отнесены принципы организации вычислений (вычислительного процесса), которые будут более эффективны на ЭВМ определенного типа, с определенной организацией.

Технический проект (дизайн) ЭВМ в узком смысле – техническая спецификация конкретных электронных схем и компонентов программного обеспечения различного уровня (встроенного (firmware), системного и прикладного (software)), из которых построена конкретная ЭВМ или ВС, набор правил проведения инженерной разработки, которые в комплексе позволяют получить изделие (ЭВМ, ВС) определенного качества, за определенные сроки и деньги. Технический проект в узком смысле не должен в деталях определять высокоуровневые принципы устройства ЭВМ, но должен быть достаточным для ее производства и использования.

#### 1.4 Виды организации и архитектуры ЭВМ.

## 1.4.1 Виды организации ЭВМ.

Любую техническую систему, в том числе ЭВМ, можно охарактеризовать ее структурой и функцией. В связи с этим организацию систем, в частности организацию ЭВМ, принято рассматривать в двух аспектах:

- 1) Структурная организация

- 2) Функциональная организация.

Структурная и функциональная организация ЭВМ – это различный взгляд на одно и то же: на блоки/компоненты в составе ЭВМ и связи между ними.

Структурная организация ЭВМ определяет состав ЭВМ на уровне блоков (устройств, компонентов), из которых она состоит, и организацию связей между ними, на уровне интерфейсов. Не так давно в этой связи рассматривались только аппаратные блоки, но на современном этапе сюда относят и программные компоненты, как минимум компоненты системного программного обеспечения.

ЭВМ – рассматривает Функциональная организация ЭВМ с точки функционирования блоков/компонент в составе ЭВМ, то есть определяет какую функцию выполняет каждый блок/компонент, как и в каком порядке он взаимодействует с другими блоками/компонентами в рамках выполнения общей задачи на ЭВМ.

## 1.4.2 Виды архитектуры ЭВМ.

## 1.4.2.1 Уровни архитектурных описаний.

Как говорилось выше, понятие архитектуры может интерпретироваться по разному, в зависимости от решаемых разработчиком ЭВМ или пользователем ЭВМ задач. В первую очередь будет различаться уровень архитектурного представления ЭВМ.

*Высоким уровнем* представления (описания) ЭВМ будет считаться описание структуры и функций без деталей устройства аппаратуры и организации программного обеспечения.

*По мере снижения уровня* описания будут исследоваться детали внутреннего устройства ЭВМ вплоть до составления технической и технологической документации для ее производства.

Самым высоким уровнем описания архитектуры ЭВМ считают описание *организации* вычислительных процессов, реализующих заданные/выбранные алгоритмы.

На более низком уровне рассматривают архитектуру на уровнях *прикладной и системной «программных моделей ЭВМ»*, «видимых» прикладному и системному программисту.

На еще более низких уровнях рассматривается на уровнях встроенного конфигурационного кода или микропрограммного обеспечения (firmware) и на уровне схемотехники электронных схем и физической конструкции ЭВМ.

Наконец на самом низком уровне рассматривают технологию производства электронных и конструктивных компонент.

## 1.4.2.2 Программная и аппаратная архитектуры.

Существует достаточно много классификаций архитектурных представлений.

Естественным, часто применяемым на практике подходом к классификации архитектур ЭВМ (одним из сторонников подобного подхода к классификации архитектуры является В. Л. Григорьев.):

- 1) программная архитектура, которая включает в себя аспекты, видимые и важные для программиста.

- 2) аппаратная архитектура, которая включает в себя аспекты, связанные с аппаратными средствами, **не**видимые программистом (прозрачные как для программиста, так и для программ), но оказывающие влияние на способ и эффективность использования ЭВМ, прежде всего на организацию программного обеспечения (см. п.1.3.3).

Программную архитектуру также можно разделить на два уровня: *прикладную* и *системную*, что связано со сложившимся различием проблем и приоритетов в работе системных и прикладных программистов.

В соответствии с рассмотренным выше принципом разделения понятий *архитектура* ЭВМ и *организация* ЭВМ, а также с разделением архитектуры ЭВМ на программную и аппаратную, можно сопоставить понятия *аппаратная архитектура* ЭВМ и *структурная организация* ЭВМ.

## 1.4.2.3 Instruction Set Architecture, ISA – архитектура системы команд.

Архитектура системы команд (Instruction Set Architecture, ISA) относится к классу программных архитектур. Она представляет собой описание средств ЭВМ (команд. регистров, памяти и других), которые доступны программисту на уровне машинных команд (самый низкий уровень программирования). ISA является спецификацией аппаратуры для программиста (можно сказать. что ISA задает границу между аппаратурой и программными средствами ЭВМ) и соответственно ISA – обязательная часть описания любого процессора, определяющая, как его использовать. Более подробно ISA будет рассмотрена в последующих разделах.

#### 1.4.2.4 Системная архитектура.

В настоящее время в силу возросшей сложности устройства ЭВМ/ВС аспекты программной и аппаратной архитектур тесно переплелись между собой и с трудом могут быть отделены друг от друга. Это касается прежде всего специализированных систем. Например:

- в системах обработки аудио- и видеоинформации функции, описываемые на уровне прикладных программ, могут иметь полностью аппаратную реализацию и при разработке программ программист должен учитывать особенности доступа к данным аппаратным функциональным блокам и доступность этих блоков в каждый момент времени.

- в быстродействующем телекоммуникационном оборудовании в зависимости от необходимоти поддержки того или иного сетевого протокола генерироваться/подключаться соответствующие специализированные аппаратные процессоры. Если какого либо протокола не требуется, то соответствующие процессоры «стираются» из аппаратуры, а на их месте создаются процессоры другого типа. Такое стало возможным только в последнее время после появления мощной динамически реконфигурируемой аппаратуры – ПЛИС.

Таким образом, выделяют не только аппаратную и программную архитектуры, но и системную архитектуру, которая располагается над аппаратной и программной, описывает, из каких функциональных блоков состоит ЭВМ, как они объединены, но не указывает способ их реализации – аппаратный или программный.

#### 1.4.3 Обобщенное представление архитектуры и организации ЭВМ и их аспектов.

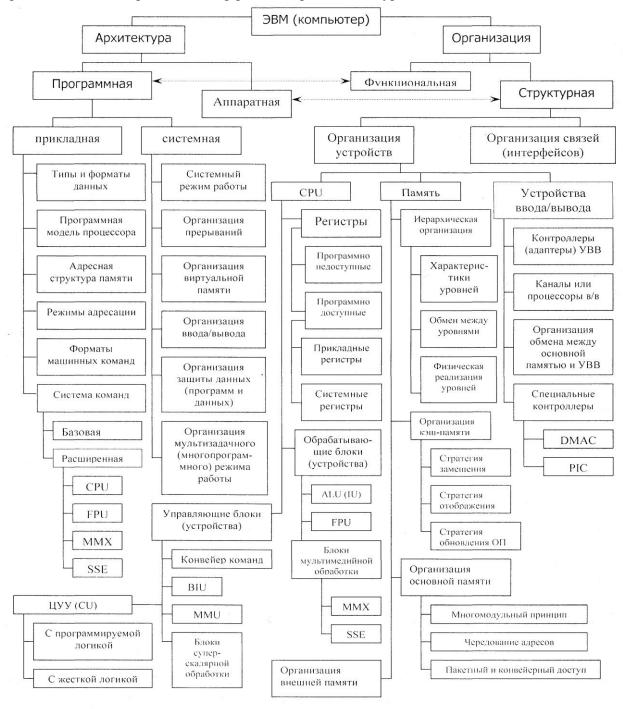

В соответствии классификацией, приведенной в предыдущих разделах, можно предложить структуру аспектов организации и архитектуры ЭВМ, изображенную на рисунке (см. Рисунок 1).

К основным элементам (аспектам) прикладной программной архитектуры (прежде всего архитектуры уровня системы команд - ISA), как правило, относят:

- типы, форматы и способы представления данных, аппаратно поддерживаемые в ЭВМ:

- регистровая структура процессора;

- адресная структура основной памяти и принципы размещения информации в ней, принципы формирования физического адреса;

- режимы адресации;

- структуры и форматы машинных команд;

- система команд.

Все аспекты прикладной архитектуры входят и в системную архитектуру.

К дополнительным аспектам системной программной архитектуры, как правило, относятся:

- организация прерываний;

- организация ввода/вывода;

- организация виртуальной памяти (сегментная и страничная), принципы преобразования логического (виртуального) адреса в физический;

- организация защиты памяти;

- организация многозадачного (многопрограммного) режима работы ЭВМ, организация переключения задач (программ);

- поддержка механизмов отладки программ на аппаратном уровне;

- поддержка механизмов проверки (тестирования) отдельных блоков процессора на аппаратном уровне.

К основным аспектам аппаратной архитектуры, как правило, относятся:

структурная организация ЭВМ, включающая в себя номенклатуру устройств, входящих в состав ЭВМ, и организацию связей между устройствами на уровне аппаратных интерфейсов;

- структурная организация процессора, включающая в себя реализацию конвейера команд и арифметико-логического устройства и принципы построения блока микропрограммного управления;

- организация кэш-памяти;

- организация основной памяти на физическом уровне и, в частности, принципы построения многомодульной памяти с расслоением обращений (чередованием адресов):

представление аппаратного интерфейса на физическом уровне.

Рисунок 1 Обобщенное представление архитектуры и организации ЭВМ.

**CPU** - Central Processing Unit - Центральное устройство обработки, Центральный процессор

FPU - Floating Point Unit - Устройство обработки с плавающей точкой

MMX - Multi Media Extension - Мультимедийное расширение

SSE - Streaming SIMD Extension - Потоковое SIMD расширение

SIMD - Single Instruction Multiple Data - Одиночный поток команд и многопотоковых данных

ALU - Arifmetic and logic Unit - Арифметическое и логическое устройство

IU - Integer Unit - Целочисленное устройство

MMU - Memory Management Unit - Устройство (блок) управления памятью

BIU - Bus Interface Unit - Интерфейсный блок (устройство)

DM AC - Direct Memory Access Controller - Контроллер прямого доступа памяти

PIC - Programmable Interrupt Controller - Программируемый контроллер прерывания

CU - Central Unit - Устройство (блок) управления

## 2 Организация ЭВМ

## 2.1 Логическая организация ЭВМ

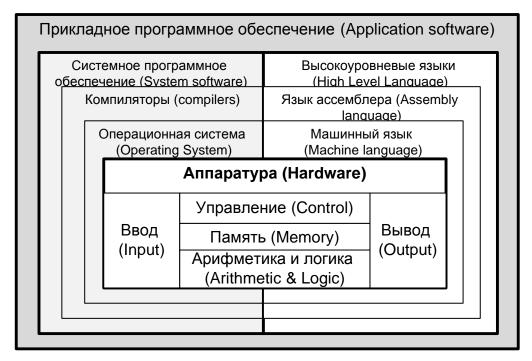

Логическая организация ЭВМ (т.е. представление связанных структурнофункциональных компонент) представлена на рисунке (см. Рисунок 2).

Рисунок 2 Логическая организация ЭВМ

Можно рассматривать два варианта логического представления ЭВМ: как иерархию программных и аппаратных подсистем (см. левую часть рисунка) и как иерархию виртуальных машин, взаимнопреобразующихся друг в друга (см. правую часть рисунка). Так как эти представления тесно связаны и зависят друг от друга, то они изображены на одном рисунке.

#### 2.1.1 ЭВМ как иерархия программных и аппаратных компонент.

*Annapamypa* (аппаратные средства, аппаратное обеспечение, hardware<sup>2</sup>) является физической основой ЭВМ. Это цифровая электрическая схема, состоящая из нескольких подсистем. Говорят, что аппаратные компоненты находятся *на нижнем уровне* организации ЭВМ.

Типовыми аппаратными подсистемами ЭВМ являются:

- процессор, включающий устройство выполнения арифметических и логических операций над данными и устройство управления, осуществляющее декодирование машинных команд и управление работой арифметическо-логического устройства;

- память, в которой хранятся программы и данные;

\_

<sup>&</sup>lt;sup>2</sup> Строго говоря, термин HARDWARE обозначает не только аппаратуру, а все неизменяемые пользователем части ЭВМ, например, аппаратные средства с «зашитой» микропрограммой.

- подсистемы ввода и вывода, отвечающие за взаимодействие процессора с «внешним» миром: с человеком (посредством монитора, звуковой системы, клавиатуры и других устройств человеко-машинного интерфейса (Human-Machine Interface, HMI)), с окружающей физической средой (посредством датчиков и исполнительных устройств двигателей, ламп, реле и т.п.)

Аппаратные блоки ЭВМ (процессор, сопроцессоры) могут исполнять только машинные команды. Кроме того, их устройство и управление ими очень сложно. Поэтому реализовывать прикладные алгоритмы (например, графический редактор на ПК) в виде программ из машинных команд фактически невозможно для человека. Поэтому между прикладными программами и аппаратурой ЭВМ имеется специальная «прослойка» системное программное обеспечение.

В различных ЭВМ используются много разных типов системного программного обеспечения, но два типа являются центральными:

- 1) операционная систем (operating system);

- 2) компилятор (compiler).

Операционная система (ОС) – это системное программное обеспечение, которое обеспечивает интерфейс между пользовательскими программами и аппаратурой, а также отвечает за управление работой аппаратуры и распределение ее ресурсов между программами. Типовыми функциями ОС являются:

- поддержка операций ввода и вывода;

- распределение системной и внешней памяти между программами;

- управление одновременным исполнением на ЭВМ нескольких программ (задач);

- организация взаимодействия нескольких ЭВМ по сети.

Компилятор – отвечает за преобразование (трансляцию) программ на языках высокого уровня (пригодных для написания программ человеком) в программы из машинных команд (в машинные коды). Кроме того, компиляторы преобразуют программные операции в команды операционных систем: поэтому на рисунке они изображены «над» операционной системой. Трансляция обычно выполняется в несколько этапов: программы на высокоуровневом языке (например, на С++) преобразуются в программы на языке ассемблера, а они в свою очередь конвертируются в машинные коды. Или в три этапа: Java – Java Byte Code – Ассемблер – машинные коды.

Компиляторы могут выполнять преобразование предварительно - перед запуском программ на исполнение. Такой режим называют offline-компиляция или просто компиляция. Другой вариант компиляции – преобразование «на лету», в процессе исполнения высокоуровневой программы. Такой способ называется online-компиляцией или трансляцией.

В любом случае компилятор является обязательным (явным - online или неявным offline) компонентом системного программного обеспечения, от которого зависит каким образом прикладной алгоритм (в виде программы) будет понят ЭВМ.

Прикладное программное обеспечение (application software) – это программа на языке высокого уровня, реализующая прикладной алгоритм (задачу). Для прикладной программы скрыты особенности внутренней организации ЭВМ (аппаратуры, системного ПО); она использует операции и форматы данных, определенные спецификацией высокоуровневого языка.

## 2.1.2 ЭВМ как иерархия виртуальных машин.

Другой взгляд на ЭВМ – как на иерархию программируемых ВМ с различной системой команд (языками) и организацией вычислительных средств (памяти, регистров и т.п.) В процессе поэтапной компиляции программ осуществляется переход от более высокоуровневой ВМ к низкоуровневой и так до аппаратуры - до физической ВМ.

На верхнем уровне языком ВМ является высокоуровневый язык программирования (C, C++, Java и т.п.) плюс набор команд (вызовов) операционной системы. Форматы данных и наборы операций также определяются спецификацией высокоуровневого языка. Программы пишет человек в соответствии с реализуемым им прикладным алгоритмом.

Высокоуровневых языковых ВМ может использоваться одна или несколько.

Ниже находится ВМ с языком ассемблера. Организация этой ВМ максимально близка к организации физической ВМ: такой же набор регистров, памяти. Основные отличия: использование символьных идентификаторов для команд и данных, поддерживается модульная организация программ и т.п.

Под BM в иерархии ассемблера располагается BM с системой машинных команд. Это физическая BM, как она доступна для программирования.

Ниже располагаются аппаратные средства ЭВМ. Однако (хоть это и «не видно» программисту), они «внутри» так же организованы как иерархия ВМ, имеющая несколько НЕОБЯЗАТЕЛЬНЫХ (кроме нижнего) уровней:

- уровень настроек для аппаратных функциональных блоков (таймеров, контроллеров и т.п.);

- уровень микропрограмм;

- уровень конфигураций («прошивок») для аппаратной платформы (например, для ПЛИС);

- уровень физической цифровой схемы НЕИЗМЕНЯЕМЫЙ.

Так как все уровни выше уровня машинных команд не имеют в основе реальных аппаратных средств, воспринимающих соответствующий язык команд, то их называют виртуальными ВМ (ВВМ).

Уровни включая и ниже уровня машинных команд относятся к классу *реальных ВМ* (PBM). Для большинства пользователей — программистов единственной реальной ВМ является ВМ уровня машинных команд<sup>3</sup>.

## 2.1.3 Связь вариантов представления ЭВМ.

Рассмотренные выше варианты представления ЭВМ имеют жесткую взаимозависимость:

- 1) Взаимное преобразование виртуальных ВМ выполняется при помощи системного программного обеспечения: компиляторов (в процессе трансляции или компиляции) и операционных систем (в процессе обработки команды для ОС и управления ресурсами ЭВМ для прикладных программ).

- 2) Уровень РВМ обычно ассоциируется с уровнем аппаратуры ЭВМ, как физической (реальной) основы ЭВМ.

Исходя из этого при разработке ЭВМ эти два представления организации ЭВМ следует рассматривать взаимосвязано.

## 2.2 Структурно-функциональный базис ЭВМ

Основой большинства современных ЭВМ является цифровая электронная аппаратура — цифровые схемы. Данные схемы строятся на элементной базе - элементарных аппаратных

<sup>3</sup> Если оценивать понятия реальной и виртуальной ВМ в более широком смысле, то мы можем установить, что нет четко определенных уровней ВВМ и РВМ – все должно рассматриваться относительно доступных возможностей программирования ВМ.

Если при разработке программного обеспечения на данном уровне программный код ВМ изменяется, то это уровень ВВМ. Если не изменяется – РВМ. Например: Если мы берем ПЛИС, записываем в нее прошивку «микропроцессор» (т.е. она работает как микропроцессор) и отдаем программисту для разработки программ, то для него уровнем РВМ будет уровень машинных операций микропроцессора. Если же пытаться делать обработку прикладных данных аппаратно путем разработки специальных аппаратных блоков на ПЛИС, то уровнем РВМ станет уровень конфигурирования ПЛИС.

функциональных элементах, выполненные в современной интегральной технологии (в виде интегральных микросхем, ИМС).

В соответствии с иерархическим подходом, принятым при проектировании сложных систем, аппаратная элементная база также может быть разделена на уровни:

- 1) Нижний уровень вентильный: логические элементы (вентили) И, ИЛИ, НЕ и т.п., и запоминающие элементы – триггеры.

- 2) Средний уровень базовых операционных элементов: элементы выполнения арифметических операций - сумматоры, АЛУ; многоразрядные запоминающие элементы - регистры, адресуемая регистровая память, счетчики; элементы коммутации и управления коммутацией – мультиплексоры, шины, шифраторы, дешифраторы.

- 3) Высокий уровень функциональных блоков: РАЛУ, умножители, массивы памяти, порты ввода-вывода.

- 4) Сверхвысокий уровень подсистем: процессор, блоки и устройства памяти, контроллеры интерфейсов и т.п.

В реальном проектировании нет четких границ между уровнями, на любом этапе могут возникнуть задачи, которые требуют более детальной проработки на более низких уровнях, или доступны уже существующие высокоуровневые решения.

## 2.2.1 Вентильный уровень.

## 2.2.2 Уровень базовых операционных элементов.

Базовые операционные элементы (БОЭ) – функционально завершенные цифровые схемы, которые выполняют обработку многоразрядных цифровых данных (слов). БОЭ в составе структурно-функциональных и электрических принципиальных схем ЭВМ выступают как законченные элементы, т.е. не представляется их внутреннее устройство.

БОЭ бывают комбинационными: в каждый момент времени значения на цифровых выходах БОЭ зависят только от значений на их входах в это же время, и последовательностными: значения на цифровых выходах БОЭ зависят от значений на их входах и от состояния схемы в предыдущие моменты времени. Для запоминания предыдущего состояния в составе последовательностных БОЭ имеются запоминающие элементы – триггеры.

Основными типами комбинационных БОЭ, применяющимися в составе процессоров и ЭВМ являются:

## 2.2.2.1 Сумматор (Adder)

Сумматор выполняет арифметическое сложение и вычитание (в дополнительном коде) чисел, представленных в двоичном коде. В составе ЭВМ сумматор является ядром арифметико-логического устройства (АЛУ). На базе сумматора строятся также схемы умножения и деления (обычного и ускоренного).

Полусумматор (half-adder) – складывает два однобитовых операнда (A и B), выдает однобитовую сумму (S) и однобитовый перенос (C).

Полный сумматор (full-adder) – складывает два однобитовых операнда (А и В) и бит входящего переноса (C), выдает однобитовую сумму (S) и однобитовый перенос (C). Полный сумматор строится из двух полусумматоров.

Многоразрядный сумматор со сквозным переносом (ripple-carry adder) — складывает многоразрядные числа, стоится из полных сумматоров и полусумматоров.

Многоразрядные сумматоры также могут быть построены по иным схемам (кроме сквозного переноса).

## 2.2.2.2 Арифметико-логическое устройство (АЛУ)

АЛУ выполняет различные логические и математические операции над несколькими операндами. Обычно у АЛУ два операнда, представленных в двоичном коде. Типовыми операциями являются логические И, ИЛИ, НЕ; арифметические сложение, вычитание, умножение, деление; различные типы сдвигов. Выбор выполняемой операции осуществляется подачей кода на специальные управляющие входы. По результатам выполнения операций формируются специальные признаки – флаги – характеризующие результат. Например, флаги Zero (нулевой результат), Carry (перенос), Parity (четность) и другие.

АЛУ является составным БОЭ: включает сумматор, дешифраторы, мультиплексоры, комбинационные схемы установки флагов и другие составные части.

## 2.2.2.3 Дешифратор (Decoder)

Дешифратор - схема, которая преобразует входной многоразрядный код в отличный от него выходной многоразрядный код с равным или большим количеством разрядов.

В вычислительных устройствах наиболее применяем двоичный дешифратор «N в 2<sup>N</sup>», преобразующий двоичный код в унитарный код «1 из N».

## 2.2.2.4 Шифратор (Encoder)

Шифратор – схема с функцией обратной дешифратору, которая преобразует входной многоразрядный код в отличный от него выходной многоразрядный код с меньшим количеством разрядов.

В вычислительных устройствах наиболее применяем двоичный приоритетный  $uudpamop < 2^N$  в N», преобразующий унитарный код «1 из N» в двоичный код.

## 2.2.2.5 Схемы преобразования специальных кодов

Это варианты дешифраторов и шифраторов, работающие со специальными типами кодов. Например, шифратор дешифратор кода Хемминга используются для хранения данных памяти с возможностью обнаружения и восстановления ошибки битов.

## 2.2.2.6 Мультиплексор (multiplexer)

Осуществляет коммутацию одного из нескольких цифровых входов на один выход. Номер подключенного входа задается двоичным кодом на специальных адресных входах мультиплексора. Входы и выходы могут быть одноразрядными или многоразрядными, т.е. коммутируется или «один бит» или многоразрядная шина.

## 2.2.2.7 Демультиплексор (demultiplexer)

Реализует функцию обратную мультиплексору: коммутацию одного входа на один из нескольких выходов. Номер подключенного выхода задается двоичным кодом на специальных адресных входах демультиплексора. Входы и выходы могут быть одноразрядными или многоразрядными, т.е. коммутируется или «один бит» или многоразрядная шина.

## 2.2.2.8 Компаратор (Comparator)

Компаратор определяет отношение между двумя цифровыми значениями (кодами). Различают компараторы равенства и компараторы отношения.

Компараторы равенства вырабатывают значение ИСТИНА (B случае ПОЗИТИВНОГО кодирования значений кодируется логической «1») на выходе в случае равенства входных кодов. Если коды не равны – на выходе ЛОЖЬ (в случае ПОЗИТИВНОГО кодирования значений кодируется логическим «0»).

Компараторы отношения вырабатывают три выходных сигнала:

- «больше» ИСТИНА если операнд А больше операнда В;

- «меньше» ИСТИНА если операнд А меньше операнда В;

- «равно» ИСТИНА если операнд А равен операнду В.

Основными элементами последовательностного типа являются:

#### 2.2.2.9 Регистры хранения (запоминающие)

Регистр хранения – это массив из нескольких триггеров с объединенными между ними управляющим входами. Соответственно, операции записи и чтения со всеми триггерами в составе регистра можно проводить одновременно (синхронно) путем соответствующих сигналов на объединенные управляющие входы.

Регистры используются для хранения многоразрядных кодов. Регистры – основной тип многоразрядных ячеек памяти в составе процессоров.

#### 2.2.2.10 Регистры сдвига

Регистры сдвига - модификация регистров хранения, которые позволяют сдвигать хранимые коды на заданное число разрядов. Сдвиг осуществляется при появлении на специальном управляющем входе импульса на один разряд. Если нужно сдвинуть на несколько разрядов - нужно подать несколько импульсов. Другой вариант - на специальном управляющем входе устанавливается значение, на которое нужно сдвинуть код, и сдвиг осуществляется сразу на нужное число разрядов. Такой способ обычно используется в составе АЛУ.

Существуют регистры сдвига вправо, влево или комбинированные. Направление сдвига выбирается отдельными управляющими сигналами.

Регистры сдвига могут использоваться в составе АЛУ (но в АЛУ чаще используются иные способы и схемы сдвига операндов). Основным применением регистров сдвига последовательная передача данных: сохраненный в регистр код последовательно передается по одноразрядной линии путем побитового сдвига из регистра.

## 2.2.2.11 Блоки адресуемых регистров

Блоки адресуемых регистров представляют собой массив регистров, объединенный с управляющей логикой – дешифратором адреса. Дешифратор адреса регистра позволяет обращаться по выбору к одному из регистров в массиве через общие входные и выходные линии. Выбор регистра осуществляется посредством подачи номера регистра – адреса – на специальные управляющие входы.

Блоки адресуемых регистров основной тип блоков хранения данных в составе процессоров.

## 2.2.2.12 Счетчики

Счетчик – тип регистра, который увеличивает или уменьшает свое значение при поступлении на специальный вход импульсов. Т.е. счетчик считает импульсы. Счетчики построены на триггерах и дополнительном блоке управляющей логики.

Счетчики классифицируются по следующим признакам:

- 1) По типу кода, в котором хранится цифровое значение:

- двоичные;

- двоично-десятичные.

- 2) По коэффициенту пересчета числовому значению, после достижения которого значение счетчика обнуляется и счет начинается с нуля.

- 3) По направлению счета:

- инкрементные;

- декрементные;

- реверсивные.

- 4) По внутренней организации несколько вариантов классификации, например, по способу переноса между разрядами хранимого кода.

Счетчики широко используются в вычислительных системах, как формирователи последовательностей синхронизирующих импульсов с определенной частотой, как

счетчики команд в процессорах, как указатели адресов при обращениях к последовательным ячейкам памяти и т.п.

## 2.3 Базовые принципы организации ЭВМ фон Неймана.

Джон фон Нейман – американский ученый венгерского происхождения. На основе критического анализа одной из первых ЭВМ ENIAC (к моменту его присоединения к проекту архитектура ENIAC уже была выбрана) им и его коллегами были сформулированы базовые принципы построения ЭВМ, обеспечивавшие ее эффективность, универсальность, развиваемость и удобство. В 1946 году фон Нейман вместе с Г.Гольдстейном и А.Берксом написал и выпустил отчет "Предварительное обсуждение логической конструкции электронной вычислительной машины", в котором были представлены данные принципы и базовая структура ЭВМ им соответствующая.

В дальнейшем, в работах фон Неймана и других специалистов эти принципы дополнялись, уточнялись, однако основные идеи не изменились до нашего времени под наименованием «принципы фон Неймана». На этих основах строятся большинство современных компьютеров, и даже в случае создания так называемых «не фон Неймановских ЭВМ» видоизменяются не все принципы, а только их часть, т.е. идейная база во много сохраняется.

## 2.3.1 Принципы фон Неймана.

Существует много вариантов «принципов фон-Неймана», полученных путем анализа комплекса его работ и работ других специалистов. Данные варианты обладают различной степенью полноты охвата аспектов организации ЭВМ. Ниже приводится, как кажется, в значительной мере полный вариант. Разделение принципов на основные и дополнительные выполнялось не по критерию времени опубликования и фактического авторства, а по принципу значимости для организации ЭВМ.

К основным принципам относим:

- 1. Принцип хранимой программы.

- 2. Принцип линейности памяти.

- 3. Принцип последовательного выполнения программы и возможности перехода.

- 4. Принцип отсутствия различий между командами и данными.

- 5. Принцип отсутствия различий в семантике данных.

К дополнительным принципам относим:

- 6. Принцип программного управления.

- 7. Принцип двоичного кодирования.

- 8. Принцип иерархической памяти.

- 9. Принцип низкоуровневости машинного языка.

- 10. Принцип микропрограммирования.

#### 2.3.2 Каноническая структура ЭВМ.

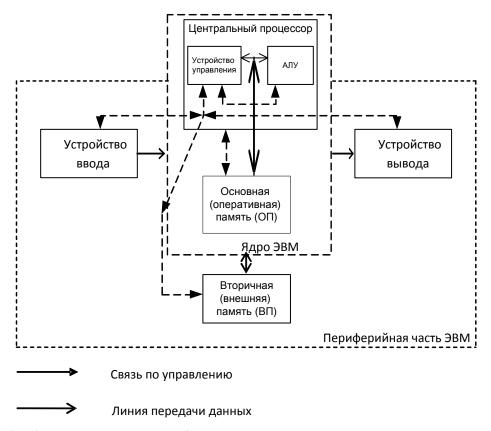

Реализация принципов Фон-Неймана базируется на использовании ЭВМ с некоторой канонической (типовой) структурой, которая также была предложена группой Фон-Неймана. Подсистемы канонической структуры являются обязательными для любых современных ЭВМ, отвечающих (целиком или частично) принципам организации Фон-Неймана. При этом реальные современные ЭВМ имеют гораздо более сложную, многоуровневую внутреннюю организацию подсистем ЭВМ и организацию связей между ними, чем в канонической структуре.

Каноническая структура ЭВМ (см.рисунок) содержит следующие подсистемы:

- центральный процессор (ЦП), включая:

- о устройство управления (УУ);

- о операционной устройство арифметико-логическое устройство (АЛУ);

- память, включая:

- о основную память (ОП);

- о вторичную (внешнюю) память (ВП);

- подсистему ввода-вывода, включая:

- о устройства ввода;

- о устройства вывода.

В целом принципы Фон-Неймана задают распределение функций между данными подсистемами и определяют правила взаимодействия подсистем между собой.

Рисунок 3 Каноническая структура ЭВМ

## 2.3.2.1 Ядро ЭВМ.

ЦП и ОП образуют центральную часть ЭВМ – *ядро ЭВМ*. Иногда ядро ЭВМ называют PMS-подсистемой (Processor-Memory-Switch). Ядро ЭВМ объединяет минимальный и обязательный набор компонентов, чтобы хранить и исполнять программу, хранить и предоставлять данные для программной обработки.

Основным центральный процессор (ЦП, СРU) является основным устройством ЭВМ, которое выполняет двойную функцию: с одной стороны ЦП является обрабатывающим устройством, т.к. выполняет функции по обработке данных в соответствии с заданной программой; с другой стороны ЦП является управляющим устройством, в связи с тем, что на него возлагаются функции: во-первых, по управлению программой, во-вторых, по управлению периферийными устройствами ЭВМ.

Управление программой подразумевает ее запуск, остановку, прерывание, обнаружение ошибок в процессе исполнения программы и реакцию на них. Управление периферийными устройствами (ПУ) со стороны ЦП, как правило, сводится к организации обмена между ПУ и ядром ЭВМ и к обеспечению реакции на запросы ПУ.

Основными устройствами (блоками) ЦП являются, во-первых, AЛУ (ALU), во-вторых, устройство управления (СU).

АЛУ (или, более широко, операционное устройство) реализует функции ЦП по обработке данных и предназначено для выполнения арифметических и логических операций над целыми числами, логическими значениями и символьными данными.

Функцией устройства управления (УУ) является выработка сигналов управления, с помощью которых осуществляется выполнение элементарных операций (которые называются микрооперациями) в АЛУ, ОП или блоках периферийной подсистемы ЭВМ.

УУ, во-первых, обеспечивает автоматическое выполнение команд программы, реализуя выборку команд из памяти, их декодирование, формирование адресов операндов и их выборку из памяти, настройку АЛУ на выполнение заданной операции и запись результата операции в память. Настройка и управление работой АЛУ, управление записью и чтением ОП реализуется посредством специальных электрических сигналов, которые генерирует УУ.

Второй функцией УУ является управление периферийными подсистемами ЭВМ, координация (синхронизация) их взаимодействия ядра и периферийных подсистем ЭВМ между собой. Для этого УУ также вырабатывает специальные управляющие электрические сигналы, подаваемые в устройства периферийной подсистемы.

#### 2.3.2.2 Периферийные подсистемы ЭВМ.

Подсистемы ЭВМ, не относящиеся к ядру, называют периферийными (под)системами. Для исполнения программ периферийные подсистемы не являются обязательными. Их функция – обеспечить обмен программами и данными между ЭВМ и «внешним» миром.

Периферийные подсистемы обеспечивают подключение ядру различных периферийных устройств, таких как:

- 1) Устройств ввода-вывода: для связи человека и ЭВМ (монитор, клавиатура, принтер и т.п.), для связи ЭВМ с физическими объектами (датчиков, управляемых электроприводов, реле и т.п.),

- 2) Устройств вторичной (внешней) памяти (НЖМД, НГМД и т.п.),

- 3) Устройств передачи данных (по каналам и сетям передачи данных).

В канонической структуре ЭВМ периферийные подсистемы и устройства делятся по направлению на подсистемы/устройства ввода и подсистемы/устройства вывода, однако на практике это в основном комбинированные периферийные подсистемы.

ЭВМ Подключение периферийных устройств К периферийным подсистемам осуществляется через порты ввода-вывода (порт – множество электрических сигналов, электронных каскадов и связанных с ними процедур соединения ЭВМ и периферийных устройств).

#### 2.3.3 Принцип хранимой программы.

Суть данного принципа состоит в том, что команды управления процессом вычисления (в совокупности составляющие программу) могут быть закодированы в виде числовых значений (машинных команд) и сохраняться в памяти ЭВМ подобно данным. Из этого вытекает, что организация памяти для хранения команд и данных не имеет различий, т.е. и коды команд (программа) и данные могут храниться в одной памяти.

Отметим, что единая память для хранения программ и данных НЕ является ОСНОВНЫМ отличительным признаком архитектуры фон Неймана, как это часто упоминают. Можно говорить о двух разновидностях машин фон Неймана:

- 1) Принстонская архитектура с общей памятью программ и данных, с единым каналом доступа к этой памяти как при считывании (выборке) команд, так и при работе с данными, и с возможностью автоматической модификации программы (т.е. «из самой исполняемой программы»). Принстонская архитектура является базовой для большинства современных универсальных процессоров (x86, Power,

- 2) Гарвардская архитектура с раздельной памятью для хранения программ и данных и, соответственно, с раздельными каналами доступа к этим областям памяти, с недоступностью автоматической модификации программ.

Конечно, строго говоря, в гарвардской архитектуре есть различия для программных кодов и данных с точки зрения их хранения, что формально не соответствует принципам Фон-Неймана. Но, с другой стороны, принцип хранения программы в памяти соблюден.

В современных ЭВМ с гарвардской архитектурой программная недоступность памяти программ выполняется в ограниченном объеме: с памятью данных можно работать посредством «обычных» машинных команд, а доступ к памяти программ также может осуществляться, но в специальных режимах работы процессора или с помощью специальных ПОСЛЕДОВАТЕЛЬНОСТЕЙ команд.

Принципы гарвардской архитектуры памяти заложены:

- в организацию КЭШ-памяти многих высокопроизводительных процессоров (например, в процессорах Intel x86 начиная с Pentium существуют блоки с независимым доступом: КЭШ-команд (Instruction Cache) КЭШ-данных (Data Cache));

- в организацию основной памяти многих специализированных процессоров, прежде всего – микроконтроллеров для систем управления. Это обеспечивает высокий уровень надежности/безопасности (защита от само модификации кода) и повышение производительности при ограниченных аппаратных ресурсах.

## 2.3.4 Принцип линейности памяти.

Принцип состоит в том, что память ЭВМ представляет совокупность упорядоченных ячеек, каждая их которых идентифицируется (адресуется) индивидуальным адресом. Совокупность адресов всех ячеек образует линейное – неразрывное – адресное пространство, где ячейки памяти упорядочены по возрастанию их Соответственно память канонической Нейманновской архитектуры можно рассматривать как вектор ячеек.

Принцип линейности памяти является ключевым для организации последовательного исполнения программы с помощью счетчика команд (см. ниже) и для организации структур данных без явных указателей элементов.

Понятие «линейности» относится к способу адресации ячеек памяти, а не к способу их «физического расположения»: ячейки с соседними адресами могут располагаться «в различных углах» кристалла микросхемы памяти или даже в различных миросхемах памяти.

Само понятие «ячейки памяти» не является однозначным: с одной стороны под ним понимается совокупность запоминающих элементов (один элемент обычно хранит один бит данных), идентифицируемых одним и тем же адресом. Так как минимальной адресуемой единицей данных в большинстве современных вычислительных систем является байт из 8-ми бит (но могут быть и другие варианты), то в этом смысле байт будет рассматриваться как ячейка памяти. Такой взгляд ближе к логической организации ЭВМ.

С другой стороны, под ячейкой памяти иногда понимают совокупность запоминающих элементов, параллельно участвующих в одной и той же операции с памятью: записи или чтения. В этом смысле в ячейку будут образовывать биты, одновременно передаваемые по шине данных от или к памяти. Соответственно, если шина 16-разрядов, то и ячейка 16разрядов, если шина памяти 32-разряда – то и ячейка 32-разряда. Такой взгляд – ближе к аппаратной организации ЭВМ.

Наконец, третий взгляд: ячейка – это элемент данных в памяти адресуемый командой. В этом смысле понятие ячейки совпадет с понятием слова памяти. Такой взгляд на понятие ячейки – функциональный.

## 2.3.5 Принцип последовательного выполнения программы и возможности перехода.

Этот принцип означает, что выполнение любой программы в ЭВМ сводится к выполнению ее (программы) команд в порядке возрастания их номера – адреса расположения кода команды в памяти. Это избавляет от применения в составе команд указателей следующей команды, чем упрощает устройство выборки команды в составе процессора и экономит память на хранение программного кода.

Данный принцип управления исполнением программы также называют принципом управления потоком команд. Альтернативные принципы – управление потоком данных и потоком запросов (см. ниже).

Аппаратная поддержка принципа последовательного выполнения программы реализуется в виде счетчика команд (для его обозначения используют английские аббревиатуры IP (Instruction Pointer) или PC (Program Counter)). Счетчик команд аппаратный двоичный счетчик, увеличивающий свое значение с каждым очередным периодом сигнала синхронизации. Это значение используется как адрес следующей команды в линейно организованной памяти.

Линейная последовательность выполнения команд может быть нарушена при необходимости путем исполнения команд условного (ЈА, ЈВЕ и т.п.) или безусловного (ЈМР) перехода, команд циклов (LOOP и т.п.), команд вызова и возврата из процедур (CALL, RET). Все эти команды изменяют (переписывают) значение счетчика команд, а значит и адрес следующей исполняемой команды.

Еще одним случаем нарушения линейной последовательности исполнения команд в программе является обработка прерываний: по сути это исполнение команды вызова процедуры инициированное устройством управления процессора в специальных случаях: по аппаратным сигналам запроса прерывания, по специальным командам вызова «программных прерываний», при возникновении ошибки в работе процессора и т.п.

В современных процессорах широко используется механизм выполнение команд программы не в порядке их следования – Out of Order Execution. Однако, это не означает, что нарушен неймановский принцип последовательного выполнения команд: результаты выполненных не по порядку команд сохраняются в памяти в соответствии с заданной программой последовательностью. Для этого используется специальный блок In Order Retirement Unit. Пример такого механизма можно найти в составе процессоров серии Intel P6, начиная с модели Intel Pentium Pro.

#### 2.3.5.1 Не Нейманновские принципы управления программами.

Альтернативой Нейманновского принципа управления потоком команд являются:

- Принцип управления потоком данных, лежащий в основе потоковых ЭВМ;

- Принцип управления потоком запросов, лежащий в основе редукционных ЭВМ.

## 2.3.5.2 Мультитредовая и гипертредовая организация выполнения программ.

#### ОРГАНИЗАЦИЯ ПРОЦЕССОРА

#### 3.1 Классификация процессоров.

Существуют различные варианты классификации процессоров по различным критериям: по реализуемой модели вычислений (model of computation: управляемые потоком команд (Command Driver - фон-Неймановская архитектура), потоком данных (Data Driver), потоком запросов (Demand Driver) и др.), по составу и типу системы команд (CISC, RISC, VLIW), по уровням распараллеливания программ (параллелилизм на уровне машинных команд (ILP), параллелилизм на уровне потоков (MultiThreading), параллелилизм на уровне памяти (MPL) и др.), по месту хранения операндов.

Способ хранения операндов \_ базовая характеристика, непосредственно определяющая:

- прикладную архитектуру (архитектуру системы команд);

- аппаратную структуру процессоров.

Данная характеристика применима к процессорным архитектурам любых типов по иным вариантам классификации.

По способу хранения операндов выделяют следующие архитектуры процессоров [1]:

- 1) аккумуляторную;

- 2) регистровую;

- 3) с выделенным доступом к памяти;

- 4) стековую.

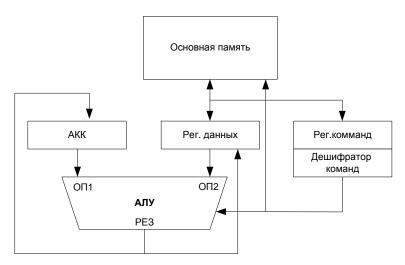

## 3.1.1 Аккумуляторная архитектура

Имеется специальный регистр аккумулятор, используемый в большинстве машинных команд как источник одного из операндов и место сохранения результата.

За счет этого в команде нужно хранить только адрес одного из операндов – адрес второго операнда и результата предопределены (это аккумулятор). Код машинной команды за счет этого становится короче, его проще декодировать. Аппаратная структура таких процессоров проста: используется только один канал для считывания данных из основной памяти, а остальные пересылки выполняются между аккумулятором и АЛУ.

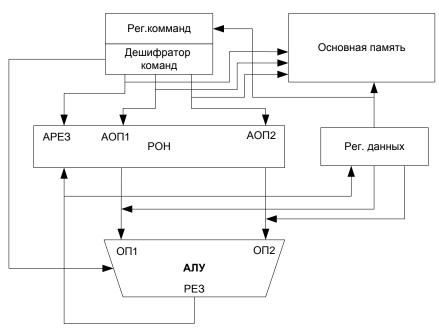

Рисунок 4 Обобщенная структура процессора с аккумуляторной организацией

Недостатком аккумуляторной архитектуры является большое количество дополнительных команда передачи данных из памяти в аккумулятор: прежде чем выполнить операцию аргумент нужно загрузить в аккумулятор.

## 3.1.2 Регистровая архитектура.

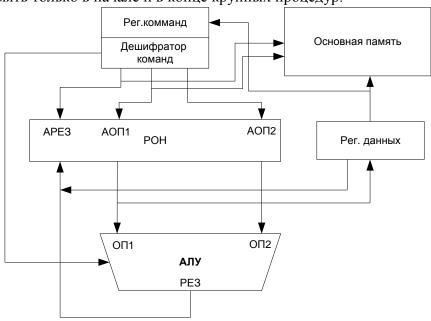

Процессор включает в себя массив регистров — регистровый файл или регистры общего назначения. Операнды и результаты могут располагаться в любом из этих регистров. Так как количество регистров относительно невелико (8-32 для CISC-процессоров, до нескольких сотен для RISC-процессоров), то адресное поле также имеет небольшой размер (порядка 3-8 бит), что позволяет в одной команде указывать адреса 2-3 операндов/результатов. Как и в аккумуляторной архитектуре, прежде чем обрабатывать операнды, их нужно загрузить в регистровый файл из основной памяти. Однако многие процессоры поддерживают арифметические и логические операции не только типа «регистр-регистр», но также «регистр-память» и даже «память-память». Такие операции выполняются медленнее (требуется загрузка/сохранение операндов из/в памяти), но позволяют получить более компактный код (одна команда вместо нескольких).

Аппаратная структура регистровых процессоров более сложная чем для аккумуляторной архитектуры: кроме самого регистрового файла требуется более сложный декодер команд, устройство формирования физических адресов для регистрового файла, более многочисленными и разветвленными становятся каналы (шины) передачи данных между блоками внутри процессора. Например, между АЛУ и регистровым файлом должно быть минимум три шины: две для чтения операндов и одна для записи результатов.

Рисунок 5 Обобщенная структура процессора с регистровой организацией

На практике наиболее часто используется именно регистровая архитектура, а также смешанная регистрово-аккумуляторная архитектура.

### 3.1.3 Архитектура с выделенным доступом к памяти.

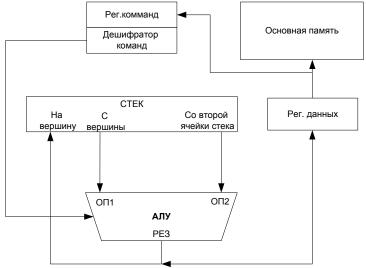

Данная архитектура является развитием регистровой архитектуры, которая обеспечивает упрощение внутренней структуры процессора, для уменьшения размера и унификации формата команд. Команды обработки данных могут работать ТОЛЬКО с регистрами. Обрабатывающие команды типа регистр-память и память-память не допускаются. Перед/после обработкой(-и) данные должны быть загружены из памяти с помощью специальных команд LOAD и STORE, подобно аккумуляторной архитектуре. Так как в данных командах максимум два (вместо трех) операнда, то на адрес памяти можно выделить в два раза большее поле, не наращивая размер команды. Чтобы минимизировать число пересылок с памятью, делают регистровый файл относительно большого объема (несколько сот байт), так что операнды и результаты пересылаются из(в) память только в начале и в конце крупных процедур.

Рисунок 6 Обобщенная структура процессора с выделенным доступом к памяти

Архитектура память-память (или Load/Store architecture) реализована во многих современных RISC-процессорах (SPARC, MIPS и др.)

## 3.1.4 Стековая архитектура.

Данная архитектура стоит несколько особняком. Стек – регистровый файл (блок памяти) работающий по принципу LIFO (последний вошел – первый вышел). В архитектуре процессора стек используется в качестве регистрового файла, подобно иным типам процессоров. При этом данные в стек записываются/считываются из основной памяти с помощью команд push и pop.

Особенностью стековых машин является то, что для выполнения операций в стековых машинах требует сохранение данных в стеке в специальном порядке, в соответствии с дисциплиной доступа LIFO. Данный порядок сохранения данных и выполнения операций называется обратная польская запись (разработана польским математиком Я.Лукашевичем). Например, выражение a=a+b+a\*c будет записано как a=ab+ac\*+ и в таком же порядке выполняются загрузки в стек и выполнение операций.

Рисунок 7 Обобщенная структура стекового процессора

Достоинством стековой архитектуры является малый размер кода команды (нет адресной части, кроме команд обмена между стеком и памятью), наличие формальных методов компиляции программ (через аппарат обратной польской записи). Также стековая машина имеет простую аппаратную структуру.

Недостатком стековой машины является наличие узкого места — стека, отсутствие произвольного доступа к памяти, сложность оптимизации кода.

Стековые архитектуры имеют давнюю историю и последнее время вновь «возродились» в связи ростом популярности языков Java и Forth и созданием соответствующих процессоров.

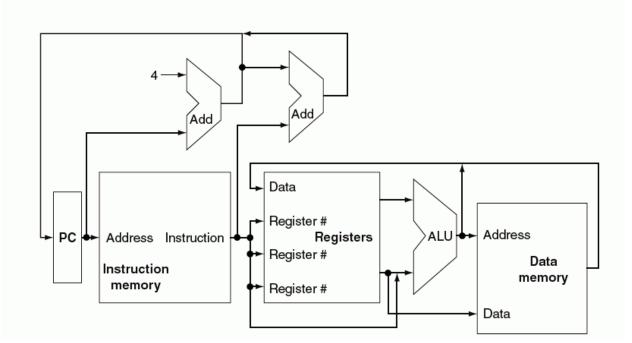

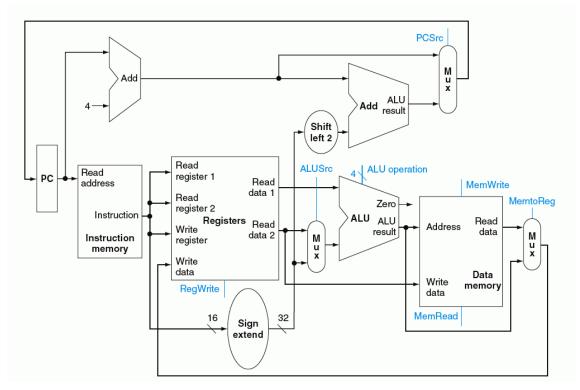

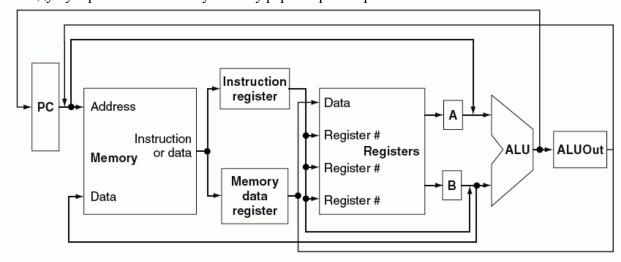

#### 3.2 Схема тракта данных (datapath) процессора.

Для общего понимания функциональной и аппаратной организации процессоров и алгоритмов исполнения машинных команд процессором, удобно использовать схему (модель) тракта данных (datapath) процессора.

Схема тракта данных – это структурно-функциональная схема, на которой показаны:

- Совокупность функциональных блоков, последовательно обрабатывающих данные. К данным относятся и обрабатываемые данные, и коды команд и адреса.

- Каналы, по которым слова данных ПОСЛЕДОВАТЕЛЬНО передаются внутри процессора от одного обрабатывающего блока к другому.

- Коммутационные блоки и сигналы, управляющие направлением и порядком передачи данных между обрабатывающими блоками.

Отличительной особенностью схем трактов данных является то, что явно показана ПОСЛЕДОВАТЕЛЬНОСТЬ обработки и передачи данных от блока к блоку и по такой схеме можно составить алгоритм исполнения машинных команд. С другой стороны. модель явно показывает аппаратную структуру процессора.

Пример обобщенной (без всех деталей организации процессора) схемы тракта данных процессора приведен на рисунке.

Рисунок 8 Обобщенная схема тракта данных процессора

В этой схеме алгоритм исполнения команд определен направленными связями между блоками и будет следующим:

- 1) Исполнение всех команд начинается с подачи адреса команды из программного счетчика PC на вход адреса (Adress) блока памяти команд (Instruction memory);

- 2) Из памяти команд через выход Instruction считывается команда.

- 3) Исполнение команды:

- а. Если выбрана команда, исполняющая операцию со значениями регистров, то из полей адресов операндов и результата адреса соответствующих регистров подаются на адресные входы (Register#) блока регистров (Registers). Далее операнды, считанные из блока регистров, подаются на вход АЛУ, выполняется требуемая операция и результат сохраняется в регистре результата через вход Data.

- b. Если выбрана команда с «непосредственным» операндом, то его значение подается на вход АЛУ «в обход» блока регистров и далее команда выполняется как в п.3.

- с. Если выбрана команда записи или чтения из памяти данных (Data Memory), то адрес для памяти данных вычисляется сложением значения базового регистра (считывается из блока регистров) и абсолютного смещения (указывается в непосредственно команде). Сложение выполняется с помощью АЛУ, полный адрес подается на вход адреса (Adress) блока памяти данных (Data Memory). Данные записываются в память данных через вход Data блока Data Memory или считываются из внешней памяти через выход блока Data Memory и записываются в регистр через вход Data блока Registers.

- d. Если выбрана команда перехода по относительному адресу, то смещение адреса подается на блок сумматора (Add) для вычисления адреса перехода.

- 4) Адрес следующей команды записывается в программный счетчик:

- а. Если выполняется следующая команда, то ее адрес рассчитывается как адрес предыдущей команды +4 (если считать, что одна команда занимает 4- е байта; если размер команды иной, то прибавляться будет другое число). Суммирование выполняется с помощью блока сумматора Add;

- b. Если выполняется переход, то записывается адрес перехода, вычисленный в соответствии с п.3.d.

Приведенная выше схема использована как сильно упрощенный пример и не определяет следующие важные аспекты организации процессора:

- 1) На один вход блока могут подаваться данные от нескольких источников (выходов других блоков). Например, на нижний вход АЛУ данные поступают с выхода блока регистров и с выхода блока памяти команд. Реальные цифровые компоненты не допускают такого подключения, так как напряжения на двух соединенных выходах могут оказаться различными и это приведет к короткому замыканию потенциалов и выходу схемы из строя.

- 2) Не определены управляющие сигналы, которые должны указывать, по какому из возможных путей выполняется передача данных в конкретный момент (это зависит от выполняемой команды), и должны настраивать реконфигурируемые операционные блоки (например, АЛУ) на выполнение требуемой в данный момент операции (например, для АЛУ: сложение, вычитание, умножение, деление или слвиг).

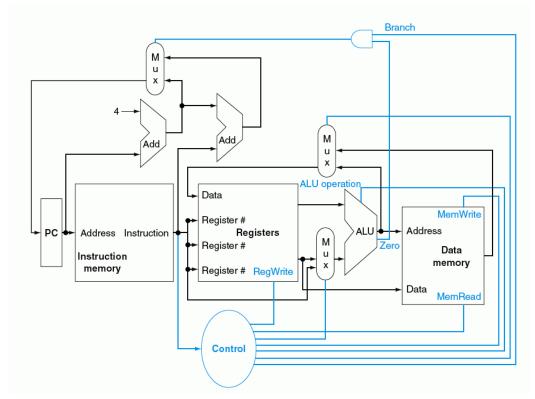

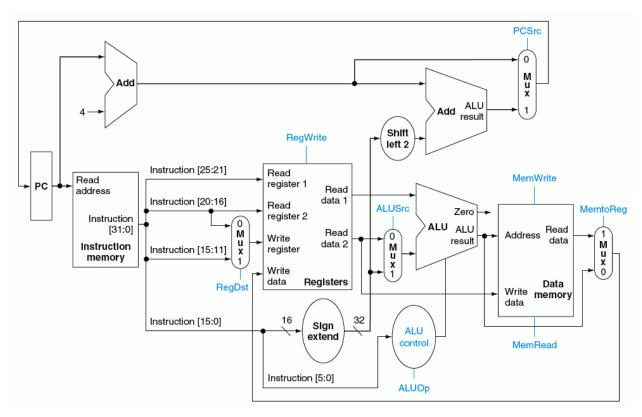

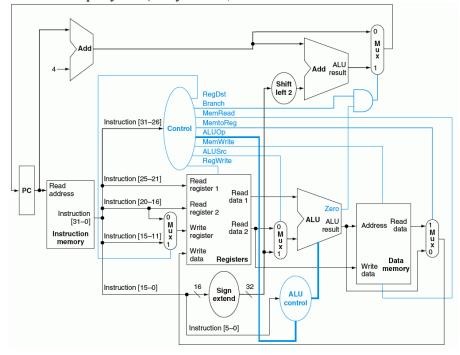

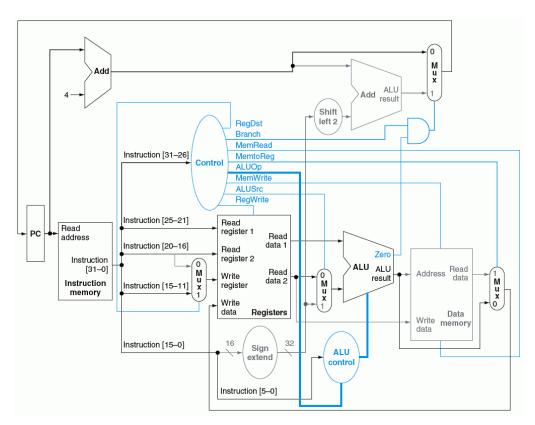

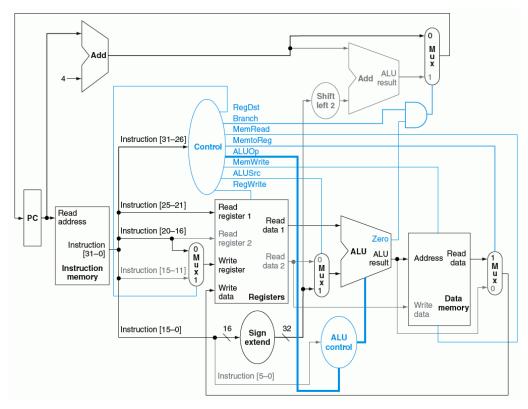

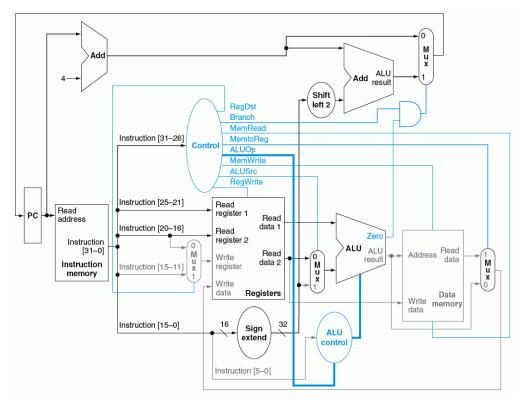

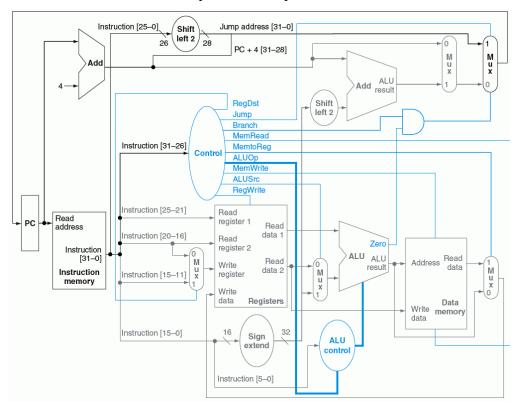

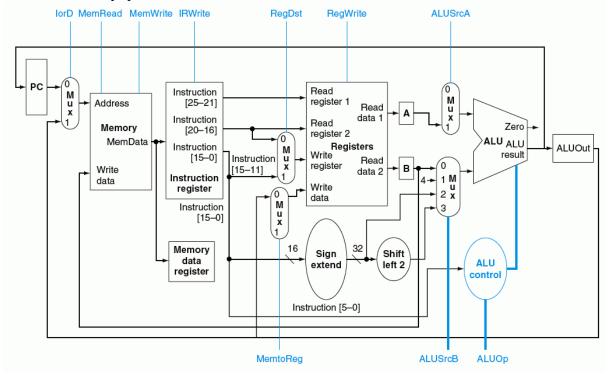

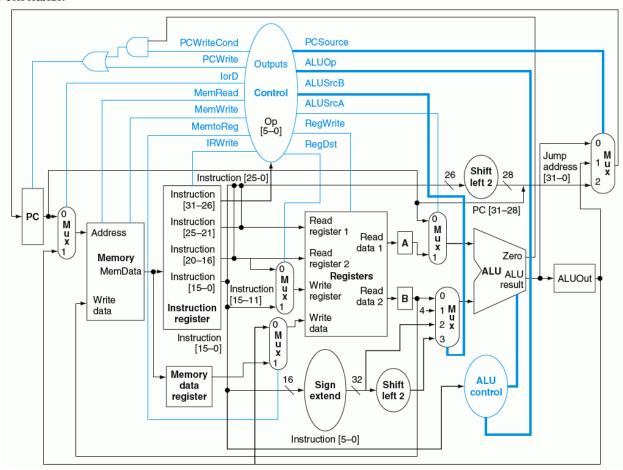

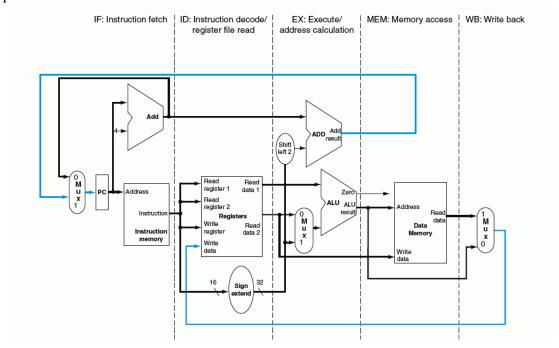

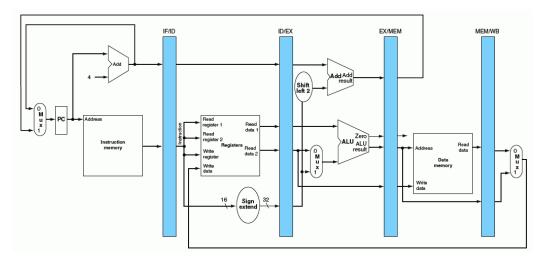

Более детальный вариант тракта данных, в котором устранены эти недостатки, приведен на рисунке ниже. Здесь выбор источников для входов функциональных блоков выполняется при помощи мультиплексоров (MUX), а также приведены управляющие сигналы для мультиплексоров, АЛУ, блоков регистров и памяти. В целом за корректную последовательность подачи управляющих сигналов отвечает специальный блок управления Control. Данный вариант будет подробно рассмотрен ниже.

Рисунок 9 Детализированная схема тракта данных процессора.

#### Компоненты тракта данных процессора.

Далее будут рассмотрены основные компоненты тракта данных процессора функциональные блоки в составе процессоров. Данный набор блоков не является полным: могут использоваться иные типы блоков, но представленные являются ключевыми, применяемыми фактически в любом процессорном ядре.

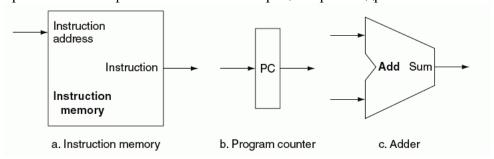

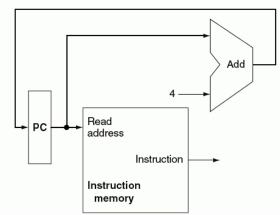

Рисунок 10 Функциональные блоки процессора: память команд (а), счетчик команд (b), сумматор (с).

#### 3.3.1 Память команд (Instruction memory).

Память команд (см. Рисунок 13) предназначена для хранения кодов команд исполняемых процессором. Имеет один многоразрядный адресный вход (входной порт), на который подается адрес расположения команды в памяти, и выход, через который считывается команда. Процесс определения адреса команды и считывания команды из памяти называется выборка команды.

## 3.3.2 Сумматор (Adder).

Сумматор – осуществляет арифметическое сложение двух двоичных чисел. Сумматор - комбинационная цифровая схема. Сумматор можно рассматривать как упрощенное АЛУ, на управляющем порту которого постоянно установлен код операции сложения. В составе процессора сумматоры как отдельные (не в составе АЛУ) функциональные блоки используются, например, для вычисления физического адреса в памяти данных из базового адреса и смещения, для увеличения (инкремента) счетчика команд, особенно в CISC-процессорах с переменной длиной команды и в других случаях.

### 3.3.3 Счетчик команд

Счетчик команд (см. Рисунок 10), англ. аббревиатуры IP (Instruction Pointer) или PC (Program counter) - специальный регистр, содержащий адрес текущей команды (инструкции), по которому эта команда считывается (выбирается) из памяти команд (памяти программ). С точки зрения функции счетчик команд правильнее называть указателем команд (IP).

В режиме последовательной выборки команд счетчик команд после выборки очередной команды увеличивается на размер команды, чтобы при следующей выборке команды указывать на следующую команду. При выполнении команд перехода адрес перехода переписывается «поверх» текущего значения счетчика команд.

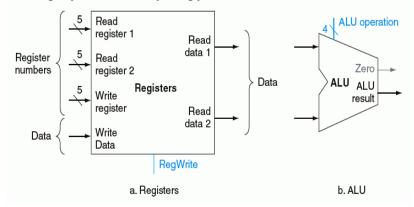

## 3.3.4 Регистровый файл.

Регистровый файл (см. Рисунок 11) - обязательный блок процессоров с регистровой организацией и их модификаций.

Регистровый файл – это блок, состоящий из нескольких регистров, предназначенных для хранения данных, обрабатываемых процессором. В каждый момент времени может совершаться операция чтения или записи только с одним регистром, адрес которого (двоичный номер регистра) подается на специальный адресный вход.

Для начального ознакомления с организацией процессора будет использован регистровый файл с несколькими параллельными трактами (под трактом понимаем адресный вход со связанным с ним входом/выходом данных) доступа к данным: два

тракта чтения данных (Read register1 + Read data1; Read register2 + Read data2) и тракт записи данных (Write register + Write data). Такая организация регистрового файла позволит выполнять операции с несколькими операндами из регистрового файла за один такт, т.е. за один такт работы процессора будут считаны два операнда из регистрового файла, обработаны (в АЛУ) и записан результат также в регистровый файл.

На практике - в реальных процессорах - регистровый файл может быть организован иным образом, например, с одним входом адреса, одним входом записываемых данных и одним выходом считываемых данных. Это значительно упрощает его электрическую схему, но потребует разделить выполнение машинных операций во времени на несколько шагов, что поведет к усложнению организации процессора.

С другой стороны, так как регистровый файл — внутренний блок процессора, участвующий в выполнении большинства машинных операций, то он должен обеспечивать высокую скорость доступа и чем меньше тактов на операцию у него будет, тем лучше.

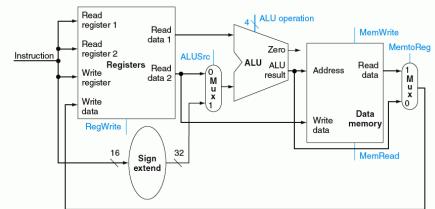

## 3.3.5 Арифметико-логическое устройство (АЛУ).

АЛУ (см.Рисунок 11) — основной блок процессора, выполняющий арифметические и логические операции. Имеет два входа для ввода операндов, один выход ALU result для считывания результатов, многоразрядный конфигурационный вход ALU operation для выборки операции (сложение, умножение, логическое сложение, сдвиг или другой), которая выполняется АЛУ в данный момент. Кроме перечисленных АЛУ обычно имеют выходы признаков результатов, например, признак нулевого результата Zero, или признак четности результата Parity и другие.

Рисунок 11 Функциональные блоки процессора: регистровый файл (а), АЛУ(b).

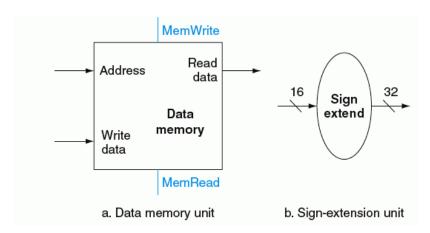

## 3.3.6 Память данных

Блок памяти данных (Data memory) (см. Рисунок 12) предназначен для хранения операндов и результатов. Его функции аналогичны регистровому файлу, но, так как память данных имеет значительный объем и соответственно большое количество разрядов шины адреса Adress, а также физически реализуется как внешний по отношению к процессору блок (отдельная микросхема или модуль), то память данных не может быть оснащена несколькими трактами данных — будет слишком много выводов у модуля памяти и слишком много связанных с ними проводников на печатной плате ЭВМ.

Поэтому память данных оснащают только совмещенным трактом данных: общий вход адреса (Adress) для записываемых и считываемых данных, один вход записываемых данных (Write data) и один вход считываемых данных (Read Data) (Такая организация портов данных также несколько упрощена: в реальных ЭВМ память обычно оснащается только одним общим портом записи/чтения данных).

Так как вход адреса общий для записи и чтения, то требуется использовать отдельные управляющие входы, показывающие, какую операцию выполняем в данный конкретный момент: запись — подается импульс на вход MemWrite или чтение — подается импульс на вход MemRead.

Рисунок 12 Функциональные блоки процессора: память данных (а), знаковый расширитель (б).

#### 3.3.7 Знаковый расширитель.

Блок знакового расширителя (Sign extend) (см. Рисунок 12) предназначен для преобразования знакового двоичного числа с меньшей разрядностью в двоичное число с большей разрядностью. Так как числа хранятся в дополнительном коде, то преобразование заключается в дублирование старшего бита во все вновь добавляемые разряды. Например, если 16-разрядное число преобразуется в 32-х разрядное, то в случае положительного числа в старшие разряды записываются «0», а в случае отрицательного числа — «1».

Изменение разрядности числа необходимо, если требуется сложение двух чисел с различной разрядностью, например (см. 3.4.1), при вычислении адреса следующей команды при выполнении команды перехода (Branch).

#### 3.3.8 Блоки сдвига (сдвигатели).

Блоки сдвига (Shift N) используются для выполнения операции сдвига на N-разрядов. Это может быть необходимо, например, в следующем случае (см. 3.4.1) (но также и в других случаях): если в команде перехода указан относительный адрес (смещение) перехода в машинных командах и при этом каждая команда состоит из нескольких байт, то сначала смещение в командах преобразуется в смещение в байтах путем перемножения размера команды на смещение в командах, а потом уже выполняется остальной расчет полного адреса перехода. Если размер команды кратен 2<sup>k</sup> (степени числа 2), то данное умножение удобно делать посредством сдвига вправо на k-разрядов, выполняемого при помощи схемы сдвига.

## 3.4 Функциональная организация однотактового процессора.

Далее будет рассмотрена организация тракта обработки данных простейшего однотактового процессора применительно к различным классам машинных операций. За тем будет рассмотрен объединенный тракт данных, реализующий инструкции различных типов.

Данная реализация тракта обработки данных предполагает:

- 1) Выполнение всех машинных операций за один такт. Это означает, что в процессе выполнения операции не выделяется нескольких последовательных шагов микроопераций.

- 2) В рамках одной машинной операции один (каждый) блок имеет только одну функцию: нельзя, например, АЛУ использовать в одной операции и для сложения операндов и для расчета физического адреса в памяти.

- 3) Один и тот же блок может иметь различное назначение при выполнении различных операций. Например, при операции сложения АЛУ используется для сложения

- операндов, а при доступе к основной памяти данных для расчета физического адреса в памяти.

- 4) При реализации различных операций функциональные блоки могут быть по разному соединены друг с другом. Для перекоммутации путей передачи данных к/от блоков используются блоки коммутации цифровых данных мультипрексоры.

- 5) Память команд и память данных раздельные.

Для демонстрации организации процессора выбрана прикладная архитектура MIPS (*Microprocessor without Interlocked Pipeline Stages* — «микропроцессор без блокировок в конвейере, разработано компанией MIPS Technologies). Архитектура MIPS – классическая RISC, регистровая с раздельным доступом к памяти, имеет фиксированный размер команды, ограниченное число типов машинных команд, ориентирована на фиксированную длительность и максимально одинаковый порядок исполнения команд всех типов (так как данная архитектура строго ориентирована на конвейерную организацию). Архитектуру MIPS можно реализовывать поэтапно: в минимальном варианте – без конвейера и далее – добавляя конвейер и иные сложные механизмы (контроллер прерываний, контроллер памяти и т.п.).

Все это делает удобной архитектуру MIPS для поэтапного ознакомления с принципами организации процессоров.

Далее будет рассмотрена реализация подмножества MIPS-системы команд для работы *с целыми числами* в следующем объеме:

- 1) Команды чтения и записи слова в основную (не регистровую) память: load word (lw), store word (sw).

- 2) Арифметические и логические команды add сложение, sub вычитание, and логическое умножение, or логическое сложение, slt (set of less that) сравнение регистра со значением.

- 3) Команды переходов: beq переход если равно, безусловный переход j.

#### 3.4.1 Инкремент счетчика команд.

Инкремент значения счетчика команд для получения адреса очередной инструкции выполняется следующим образом: используется регистр и дополнительный блок сумматора, добавляющий к текущему значению счетчика команд длину команды (для архитектуры MIPS это +4). Результат записывается в счетчик команд (см.Рисунок 13). Данный вариант механизма инкремента позволяет добавлять любые длины команд, в том числе и изменяющиеся от команды к команде (характерно для CISC-процессоров). Однако этот механизм имеет достаточно сложную структуру (включает регистр и сумматор) и функционированию (несколько шагов считывание-инкремент-запись).

Рисунок 13 Организация счетчика команд на базе регистра и сумматора

Поэтому можно использовать альтернативный вариант - схему на основе двоичного счетчика. В данном случае инкремент счетчика будет выполняться «автоматически» при подаче очередного импульса синхросигнала на счетный вход двоичного счетчика.

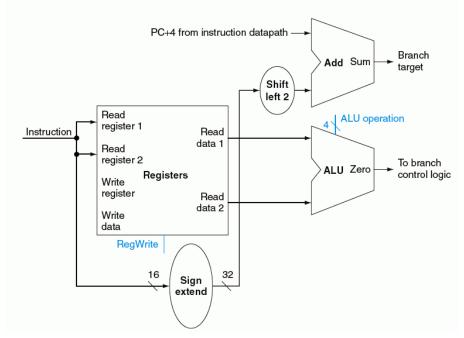

#### 3.4.2 Реализация переходов.

Команды переходов могут быть:

- 1) Условные. Будем рассматривать команду beq \$s1, \$s2, L переход на L команд относительно очередного значения счетчика команд, если равно содержимое регистров \$1 и \$2. Признаком равенства операндов будет установка флага Zero.

- 2) Безусловные. Будем рассматривать команду j L переход на L команд относительно очередного значения счетчика команд.

На рисунке (см.Рисунок 14) показан вариант тракта данных, реализующий команды переходов. Адреса сравниваемых операндов s1 и s2 подаются на адресные входы ReadRegister1 и ReadRegister2 регистрового файлаб а соответствующие значения для сравнения считываются с выходов ReadData1 и ReadData2. Эти значения подаются на вход АЛУ и сравниваются путем вычитания (или логической операции XOR). Соответствующий код операции подается на управляющий вход ALU operation. По результатам устанавливается флаг Zero (если операнды равны – «1», не равны – «0»). Полученное численное значение с выхода данных АЛУ не используется.

Переход выполняется: для команды beq если Zero = 1, для команды j — всегда. Расчет адреса перехода выполняется следующим образом. Значение L из команды является смещением следующей исполняемой команды относительно адреса текущей команды. L измеряется в командах (не в байтах), является 16-ти разрядным знаковым целым, в дополнительном коде.

Поэтому: для вычисления адреса следующей команды при выполнении команды перехода к 32-разрядному текущему значению счетчика команд нужно прибавить 16-ти разрядный относительный адрес перехода. Сначала 16-ти разрядное значение L преобразуется в 32-разрядный с помощью знакового расширителя. Далее, полученное значение приводится к байтовому адресу путем умножения на байтовый размер команды. равный 4 байта: эта операция выполняется при помощи сдвига на 2 бита влево посредством аппаратного блока сдвига Shift left 2. Наконец складываются два 32-разрядных числа (счетчик команд и смещение) и получаем полный адрес следующей команды (Вranch Target), переписываемый в счетчик команд.

Рисунок 14 Пример тракта данных для реализации команд перехода.

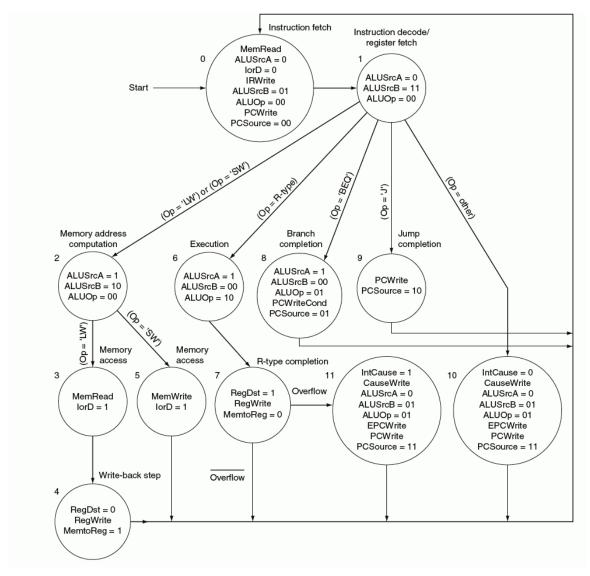

## 3.4.3 Реализация операций с регистровым файлом и основной памятью.